Toshiba: DNN Accelerator

Toshiba Electronic Devices & Storage Corporation (« Toshiba ») a annoncé aujourd’hui le développement d’un système sur puce (System on Chip, SoC) de reconnaissance d’image pour les applications automobiles qui met en œuvre un accélérateur d’apprentissage profond 10 fois plus rapide et d’une efficacité énergétique 4 fois supérieure au produit précédent de Toshiba[1]. Des détails sur la technologie ont été fournis à l'ISSCC (IEEE International Solid-State Circuits Conference) 2019 qui s’est tenue à San Francisco le 19 février.

Les réseaux neuraux profonds (Deep neural networks, DNN), des algorithmes modélisés sur les réseaux neuronaux du cerveau, effectuent un traitement de reconnaissance bien plus précis que la reconnaissance des formes et l’apprentissage machine conventionnels, et on s'attend généralement à ce qu'ils soient utilisés dans les applications automobiles. Cependant, la reconnaissance d’image basée sur les DNN avec des processeurs conventionnels prend du temps car elle repose sur un nombre considérable de calculs « multiplier-accumuler » (MAC) . En outre, les DNN avec des processeurs à haute vitesse conventionnels consomment beaucoup d’énergie.

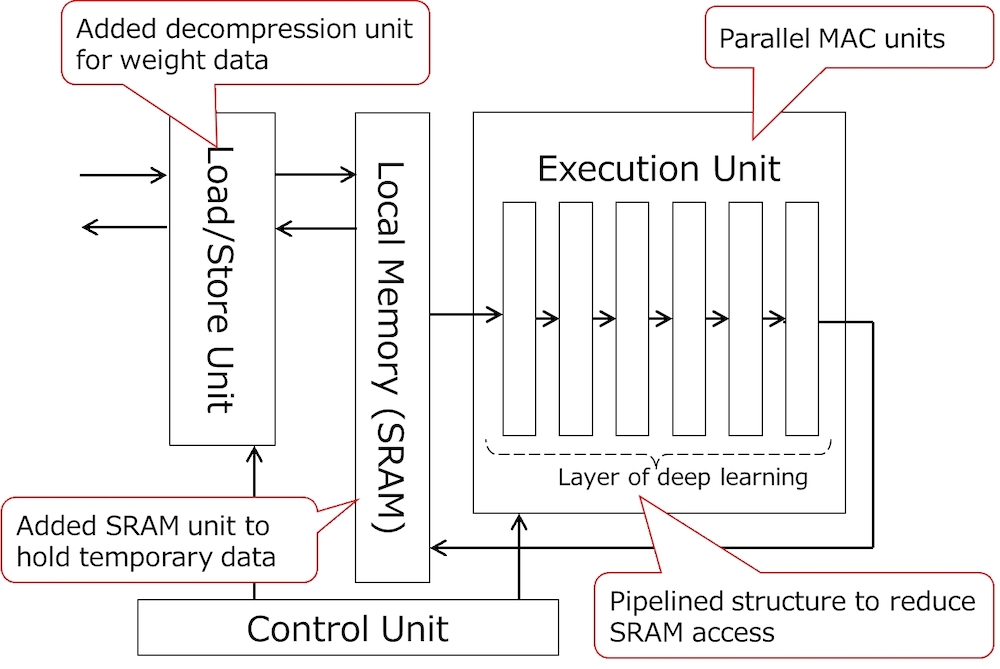

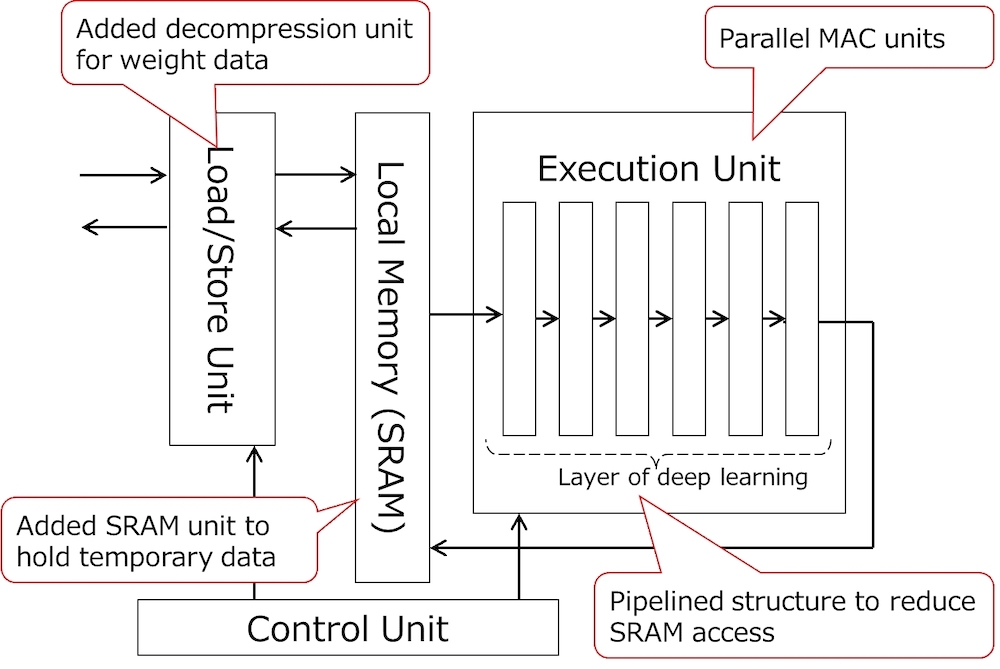

Toshiba a surmonté ce problème avec un accélérateur DNN qui met en œuvre l’apprentissage profond dans le matériel. Il a trois caractéristiques.

Des unités MAC parallèles. Le traitement DNN nécessite de nombreux calculs MAC. Le nouveau dispositif de Toshiba compte quatre processeurs, chacun avec 256 unités MAC. Cela augmente la vitesse de traitement DNN.

Un accès réduit à la mémoire DRAM. Les SoC conventionnels n’ont pas de mémoire locale pour conserver les données temporelles près de l’unité d’exécution DNN et consomment beaucoup d’énergie pour accéder à la mémoire locale. Le chargement des données de poids, utilisées pour les calculs MAC, consomme également de l'énergie. Dans le nouveau dispositif de Toshiba, des mémoires SRAM sont implémentées près de l’unité d’exécution DNN, et le traitement DNN est divisé en blocs de sous-traitement pour conserver les données temporelles dans la SRAM, réduisant ainsi l’accès à la DRAM. Par ailleurs, Toshiba a ajouté une unité de décompression à l’accélérateur. Les données de poids, compressées et stockées à l’avance dans la DRAM, sont chargées via l’unité de décompression. Cela réduit la consommation énergétique impliquée dans le chargement des données de poids depuis la DRAM.

Un accès réduit à la SRAM. L’apprentissage profond conventionnel nécessite d’accéder à la SRAM après le traitement de chaque couche de DNN, ce qui consomme trop d’énergie. L’accélérateur a une structure en couches en pipeline dans l’unité d’exécution DNN, ce qui permet à une série de calculs DNN d’être exécutés en un seul accès à la SRAM.

Le nouveau SoC est conforme à la norme mondiale de sécurité fonctionnelle pour les applications automobiles ISO26262.

Toshiba continuera d’améliorer l'efficacité énergétique et la vitesse de traitement du SoC développé et commencera ses expéditions d’échantillons du ViscontiTM5, la prochaine génération de processeurs de reconnaissance d’image de Toshiba, en septembre prochain.

Notes

[1] Le SoC de reconnaissance d’image de Toshiba dans « 1.9TOPS and 564GOPS/W Heterogeneous Multicore SoC with Color-based Object Classification Accelerator for Image-Recognition Applications », un document présenté à l'IEEE International Solid-State Circuits Conference 2015

* ViscontiTM est une marque commerciale de Toshiba Electronic Devices & Storage Corporation

* Tous les autres noms de sociétés, noms de produits et noms de services peuvent être des marques commerciales de leurs sociétés respectives.

Les réseaux neuraux profonds (Deep neural networks, DNN), des algorithmes modélisés sur les réseaux neuronaux du cerveau, effectuent un traitement de reconnaissance bien plus précis que la reconnaissance des formes et l’apprentissage machine conventionnels, et on s'attend généralement à ce qu'ils soient utilisés dans les applications automobiles. Cependant, la reconnaissance d’image basée sur les DNN avec des processeurs conventionnels prend du temps car elle repose sur un nombre considérable de calculs « multiplier-accumuler » (MAC) . En outre, les DNN avec des processeurs à haute vitesse conventionnels consomment beaucoup d’énergie.

Toshiba a surmonté ce problème avec un accélérateur DNN qui met en œuvre l’apprentissage profond dans le matériel. Il a trois caractéristiques.

Des unités MAC parallèles. Le traitement DNN nécessite de nombreux calculs MAC. Le nouveau dispositif de Toshiba compte quatre processeurs, chacun avec 256 unités MAC. Cela augmente la vitesse de traitement DNN.

Un accès réduit à la mémoire DRAM. Les SoC conventionnels n’ont pas de mémoire locale pour conserver les données temporelles près de l’unité d’exécution DNN et consomment beaucoup d’énergie pour accéder à la mémoire locale. Le chargement des données de poids, utilisées pour les calculs MAC, consomme également de l'énergie. Dans le nouveau dispositif de Toshiba, des mémoires SRAM sont implémentées près de l’unité d’exécution DNN, et le traitement DNN est divisé en blocs de sous-traitement pour conserver les données temporelles dans la SRAM, réduisant ainsi l’accès à la DRAM. Par ailleurs, Toshiba a ajouté une unité de décompression à l’accélérateur. Les données de poids, compressées et stockées à l’avance dans la DRAM, sont chargées via l’unité de décompression. Cela réduit la consommation énergétique impliquée dans le chargement des données de poids depuis la DRAM.

Un accès réduit à la SRAM. L’apprentissage profond conventionnel nécessite d’accéder à la SRAM après le traitement de chaque couche de DNN, ce qui consomme trop d’énergie. L’accélérateur a une structure en couches en pipeline dans l’unité d’exécution DNN, ce qui permet à une série de calculs DNN d’être exécutés en un seul accès à la SRAM.

Le nouveau SoC est conforme à la norme mondiale de sécurité fonctionnelle pour les applications automobiles ISO26262.

Toshiba continuera d’améliorer l'efficacité énergétique et la vitesse de traitement du SoC développé et commencera ses expéditions d’échantillons du ViscontiTM5, la prochaine génération de processeurs de reconnaissance d’image de Toshiba, en septembre prochain.

Notes

[1] Le SoC de reconnaissance d’image de Toshiba dans « 1.9TOPS and 564GOPS/W Heterogeneous Multicore SoC with Color-based Object Classification Accelerator for Image-Recognition Applications », un document présenté à l'IEEE International Solid-State Circuits Conference 2015

* ViscontiTM est une marque commerciale de Toshiba Electronic Devices & Storage Corporation

* Tous les autres noms de sociétés, noms de produits et noms de services peuvent être des marques commerciales de leurs sociétés respectives.

Autres articles

-

L’IA générative et automatisation : comment améliorer les processus business

-

Toshiba présentera une solution de stockage multimédia à l'échelle du pétaoctet à l'occasion d’IBC

-

L’automatisation du Retail : ou comment proposer une meilleure expérience aux clients

-

Toshiba Commerce France propose des services de maintenance proactive et prédictive pour améliorer la performance opérationnelle des magasins

-

De quelle façon trois générations de disques durs Toshiba ont aidé le plus grand laboratoire de physique du monde à conserver, chaque seconde, des centaines de téraoctets de données générées par les expériences du LHC